# Exp. No.6 Flip-Flops

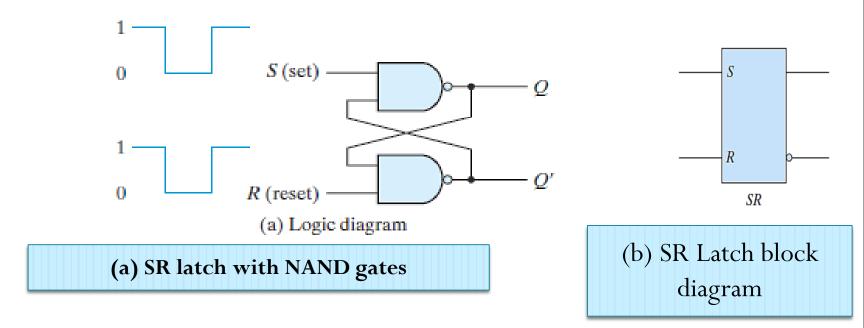

# SR- Latch (without clock)

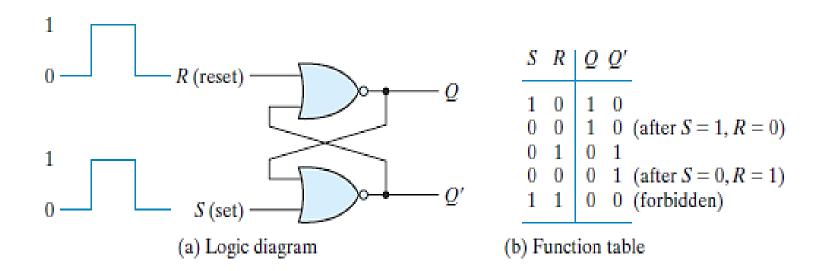

- ☐ Storage elements that operate with signal levels (rather than signal transitions) are referred to as latches; those controlled by a clock transition are flip-flops.

- ☐ Latches are said to be level sensitive devices; flip-flops are edge-sensitive devices.

• Note: Each flip flop is a binary cell capable of storing one bit of information. For example to store 4-bits we need 4 flip-flops.

SR latch with NOR gates

(a) response in latch and (b,c) clock applied to flip-flop

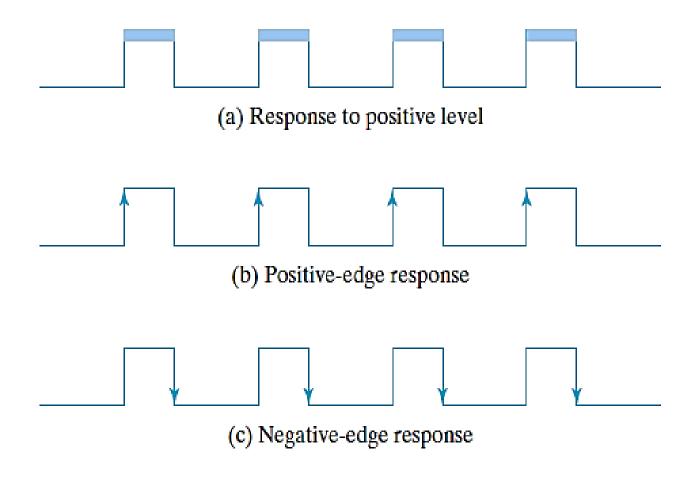

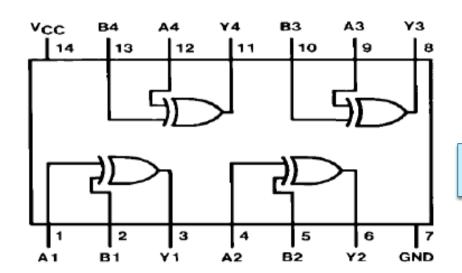

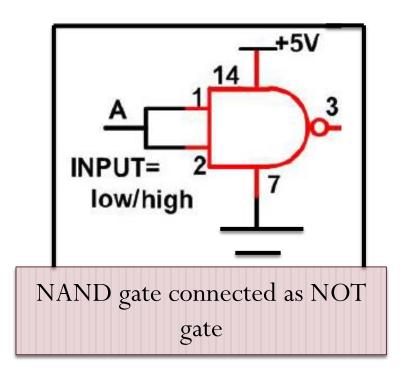

Pin diagram of 7400N NAND

Pin diagram of 7486 XOR

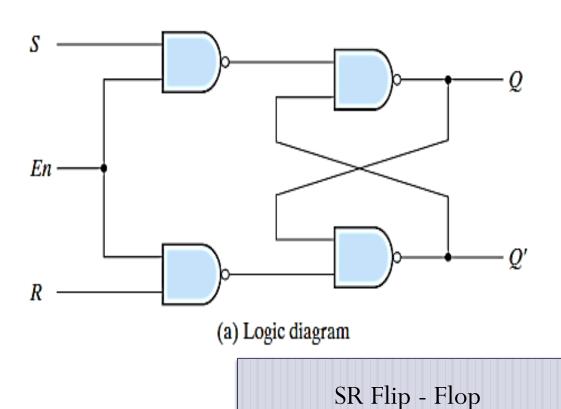

## SR Flip-Flop

• flip-flops are edge-sensitive devices and controlled by clock(clk, cp, En, Enable)

| En                    | S                | R                     | Next state of Q                                                                   |

|-----------------------|------------------|-----------------------|-----------------------------------------------------------------------------------|

| 0<br>1<br>1<br>1<br>1 | X<br>0<br>0<br>1 | X<br>0<br>1<br>0<br>1 | No change<br>No change<br>Q = 0; reset state<br>Q = 1; set state<br>Indeterminate |

(b) Function table

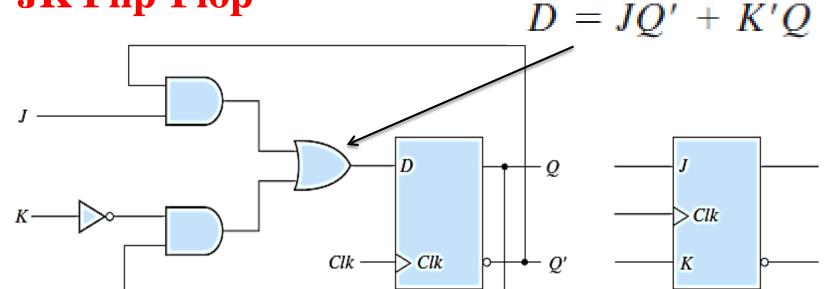

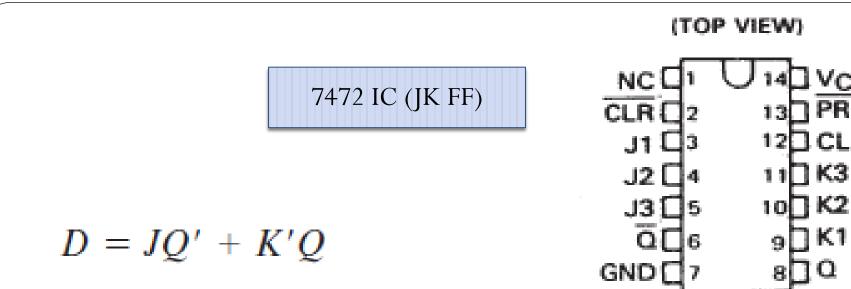

## JK Flip-Flop

(a) Circuit diagram

(b) Graphic symbol

#### JK Flip-Flop Characteristic Tables

| JK Flip-Flop |   |          |            |  |  |  |

|--------------|---|----------|------------|--|--|--|

| J            | K | Q(t + 1) | I)         |  |  |  |

| 0            | 0 | Q(t)     | No change  |  |  |  |

| 0            | 1 | 0        | Reset      |  |  |  |

| 1            | 0 | 1        | Set        |  |  |  |

| 1            | 1 | Q'(t)    | Complement |  |  |  |

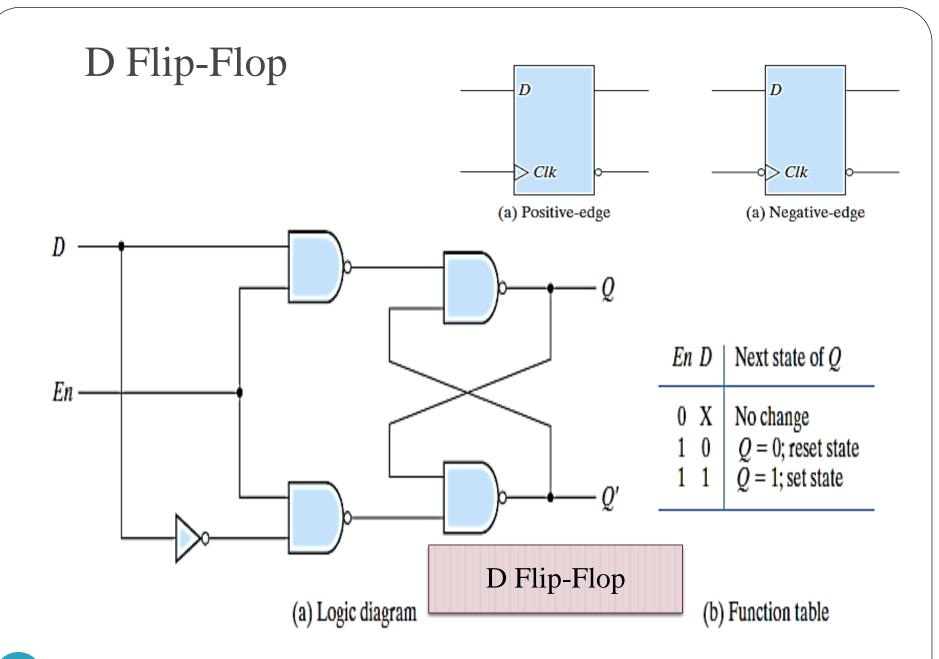

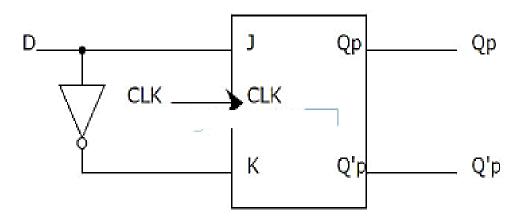

If K = D', and J = D then D = DQ' + DQ = D and the JK flip flop is connected as D Flip flop.

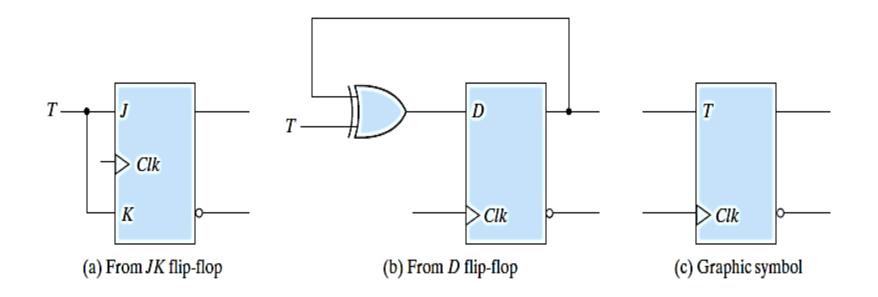

### • T Flip Flop (Toggle)

If T = 0 (J = K = 0), a clock edge does not change the output. When T = 1 (J = K = 1), a clock edge complements the output

### T Flip-Flop

| Т | Q(t+1) |            |

|---|--------|------------|

| 0 | Q(t)   | No change  |

| 1 | Q'(t)  | Complement |

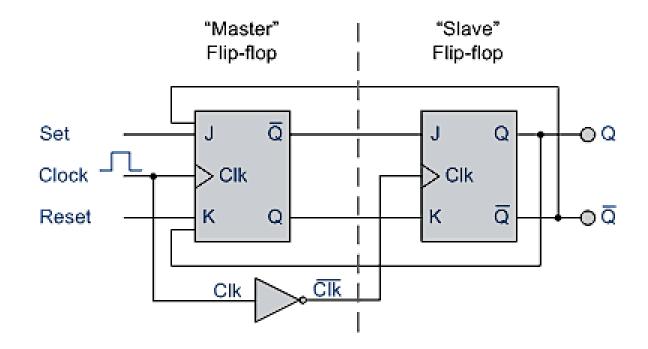

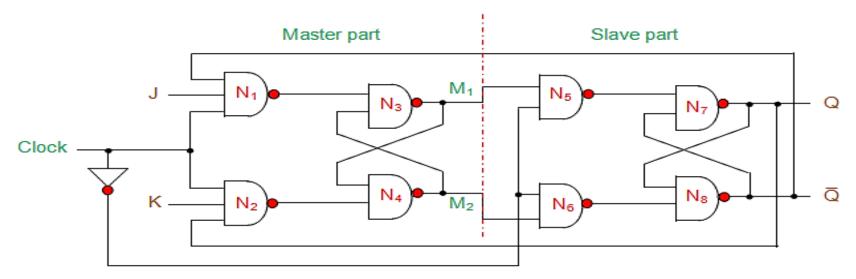

## Master-Slave JK Flip Flop

Master-slave flip flop is designed using two separate flip flops. Out of these, one acts as the master and the other as a slave.

- From the above figure you can see that both the J-K flip flops are presented in a series connection. The output of the master J-K flip flop is fed to the input of the slave J-K flip flop. The output of the slave J-K flip flop is given as a feedback to the input of the master J-K flip flop. The clock pulse [Clk] is given to the master J-K flip flop and it is sent through a NOT Gate and thus inverted before passing it to the slave J-K flip flop.

- Here the master flip-flop is triggered by the external clock pulse train while the slave is activated at its inversion i.e. if the master is positive edge-triggered, then the slave is negative-edge triggered and vice-versa.

Master-Slave JK flip-flop realized using NAND gates and an inverter

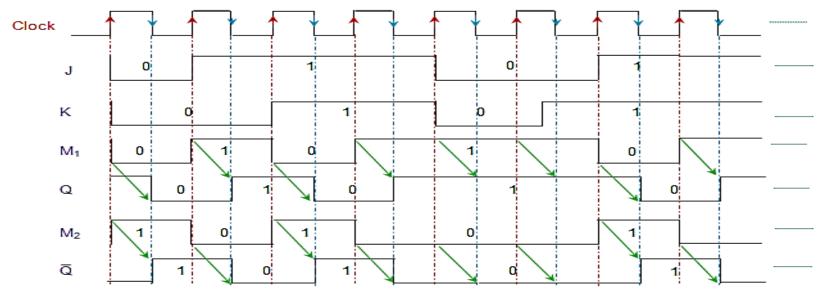

Timing diagram for master-slave JK flip-flop