# **Basic Electronics Lab Manual**

School of Physical Sciences National Institute of Science Education and Research Bhubaneswar

#### **IDENTIFICATION OF CIRCUIT COMPONENTS**

#### **Breadboards:**

In order to temporarily construct a circuit without damaging the components used to build it, we must have some sort of a platform that will both hold the components in place and provide the needed electrical connections. In the early days of electronics, most experimenters were amateur radio operators. They constructed their radio circuits on wooden breadboards. Although more sophisticated techniques and devices have been developed to make the assembly and testing of electronic circuits easier, the concept of the breadboard still remains in assembling components on a temporary platform.

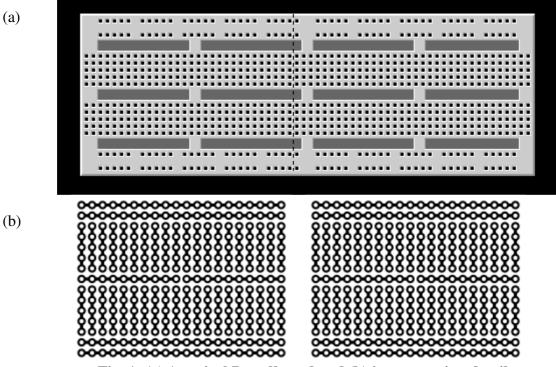

Fig. 1: (a) A typical Breadboard and (b) its connection details

A real breadboard is shown in Fig. 1(a) and the connection details on its rear side are shown in Fig. 1(b). The five holes in each individual column on either side of the central groove are electrically connected to each other, but remain insulated from all other sets of holes. In addition to the main columns of holes, however, you'll note four sets or groups of holes along the top and bottom. Each of these consists of five separate sets of five holes each, for a total of 25 holes. These groups of 25 holes are all connected together on either side of the dotted line indicated on Fig.1(a) and needs an external connection if one wishes the entire row to be connected. This makes them ideal for distributing power to multiple ICs or other circuits.

These breadboard sockets are sturdy and rugged, and can take quite a bit of handling. However, there are a few rules you need to observe, in order to extend the useful life of the electrical contacts and to avoid damage to components. These rules are:

- Always make sure power is disconnected when constructing or modifying your experimental circuit. It is possible to damage components or incur an electrical shock if you leave power connected when making changes.

- Never use larger wire as jumpers. #24 wire (used for normal telephone wiring) is an excellent choice for this application. Observe the same limitation with respect to the size of component leads.

- Whenever possible, use <sup>1</sup>/<sub>4</sub> watt resistors in your circuits. <sup>1</sup>/<sub>2</sub> watt resistors may be used when necessary; resistors of higher power ratings should never be inserted directly into a breadboard socket.

- Never force component leads into contact holes on the breadboard socket. Doing so can damage the contact and make it useless.

- Do not insert stranded wire or soldered wire into the breadboard socket. If you must have stranded wire (as with an inductor or transformer lead), solder (or use a wire nut to connect) the stranded wire to a short length of solid hookup wire, and insert only the solid wire into the breadboard.

If you follow these basic rules, your breadboard will last indefinitely, and your experimental components will last a long time.

## Resistors

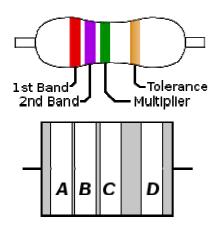

Most axial resistors use a pattern of colored stripes to indicate resistance. A 4 band identification is the most commonly used color coding scheme on all resistors. It consists of four colored bands that are painted around the body of the resistor. Resistor values are always coded in ohms ( $\Omega$ ). The color codes are given in the following table in Fig. 1.

| Band<br>Color | Digit | Multiplier  | Tolerance |

|---------------|-------|-------------|-----------|

| Black         | 0     | 1           | 1111      |

| Brown         | 1     | 10          | ±1%       |

| Red           | 2     | 100         | ±2%       |

| Orange        | 3     | 1,000       | ±3%       |

| Yellow        | 4     | 10,000      | ±4%       |

| Green         | 5     | 100,000     |           |

| Blue          | 6     | 1,000,000   | 1440      |

| Violet        | 7     | 10,000,000  |           |

| Gray          | 8     | 100,000,000 |           |

| White         | 9     |             |           |

| Gold          |       | 0.1         | ±5%       |

| Silver        |       | 0.01        | ±10%      |

| None          |       |             | ±20%      |

## **Fig. 1: Color codes of Resistors**

- band A is first significant figure of component value

- band **B** is the second significant figure

- band C is the decimal multiplier

- band **D** if present, indicates tolerance of value in percent (no color means 20%)

For example, a resistor with bands of *yellow, violet, red, and gold* will have first digit 4 (yellow in table below), second digit 7 (violet), followed by 2 (red) zeros: 4,700 ohms. Gold signifies that the tolerance is  $\pm 5\%$ , so the real resistance could lie anywhere between 4,465 and 4,935 ohms.

Tight tolerance resistors may have three bands for significant figures rather than two, and/or an additional band indicating temperature coefficient, in units of ppm/K. For large power resistors and potentiometers, the value is usually written out implicitly as "10 k $\Omega$ ", for instance.

## **Capacitors:**

You will mostly use electrolytic and ceramic capacitors for your experiments.

## **Electrolytic capacitors**

An **electrolytic capacitor** is a type of capacitor that uses an electrolyte, an ionic conducting liquid, as one of its plates, to achieve a larger capacitance per unit volume than other types.

They are used in relatively high-current and lowfrequency electrical circuits. However, the voltage applied to these capacitors must be polarized; one specified terminal must always have positive potential with respect to the other. These are of two types, axial and radial capacitors as shown in adjacent figure. The arrowed stripe indicates the polarity, with the arrows pointing towards the negative pin.

## Fig. 2:Axial and Radial Electrolytic capacitors

**Warning:** connecting electrolytic capacitors in reverse polarity can easily damage or destroy the capacitor. Most large electrolytic capacitors have the voltage, capacitance, temperature ratings, and company name written on them without having any special color coding schemes.

Axial electrolytic capacitors have connections on both ends. These are most frequently used in devices where there is no space for vertically mounted capacitors.

Radial electrolytic capacitors are like axial electrolytic ones, except both pins come out the same end. Usually that end (the "bottom end") is mounted flat against the PCB and the capacitor rises perpendicular to the PCB it is mounted on. This type of capacitor probably accounts for at least 70% of capacitors in consumer electronics.

**Ceramic capacitors** are generally non-polarized and almost as common as radial electrolytic capacitors. Generally, they use an alphanumeric marking system. The number part is the same as for resistors, except that the value represented is in pF. They may also be written out directly, for instance,  $2n^2 = 2.2$  nF.

Fig. 3: Ceramic capacitors

## **Diodes:**

A standard specification sheet usually has a brief description of the diode. Included in this description is the type of diode, the major area of application, and any special features. Of particular interest is the specific application for which the diode is suited. The manufacturer also provides a drawing of the diode which gives dimension, weight, and, if appropriate, any identification marks. In addition to the above data, the following information is also provided: a static operating table (giving spot values of parameters under fixed conditions), sometimes a characteristic curve (showing how parameters vary over the full operating range), and diode ratings (which are the limiting values of operating conditions outside which could cause diode damage). Manufacturers specify these various diode operating parameters and characteristics with "letter symbols" in accordance with fixed definitions. The following is a list, by letter symbol, of the major electrical characteristics for the rectifier and signal diodes.

## **RECTIFIER DIODES**

DC BLOCKING VOLTAGE  $[V_R]$ —the maximum reverse dc voltage that will not cause breakdown.

AVERAGE FORWARD VOLTAGE DROP  $[V_{F(AV)}]$ —the average forward voltage drop across the rectifier given at a specified forward current and temperature.

AVERAGE RECTIFIER FORWARD CURRENT  $[I_{F(AV)}]$ —the average rectified forward current at a specified temperature, usually at 60 Hz with a resistive load.

AVERAGE REVERSE CURRENT  $[I_{R(AV)}]$ —the average reverse current at a specified temperature, usually at 60 Hz.

PEAK SURGE CURRENT [I<sub>SURGE</sub>]—the peak current specified for a given number of cycles or portion of a cycle.

## SIGNAL DIODES

PEAK REVERSE VOLTAGE [PRV]—the maximum reverse voltage that can be applied before reaching the breakdown point. (PRV also applies to the rectifier diode.)

REVERSE CURRENT  $[I_R]$ —the small value of direct current that flows when a semiconductor diode has reverse bias.

MAXIMUM FORWARD VOLTAGE DROP AT INDICATED FORWARD CURRENT [V  $_F@I_F$ ]— the maximum forward voltage drop across the diode at the indicated forward current. REVERSE RECOVERY TIME [ $t_{rr}$ ]—the maximum time taken for the forward-bias diode to recover its reverse bias.

The ratings of a diode (as stated earlier) are the limiting values of operating conditions, which if exceeded could cause damage to a diode by either voltage breakdown or overheating.

The PN junction diodes are generally rated for: MAXIMUM AVERAGE FORWARD CURRENT, PEAK RECURRENT FORWARD CURRENT, MAXIMUM SURGE CURRENT, and PEAK REVERSE VOLTAGE

**Maximum average forward current** is usually given at a special temperature, usually 25° C, (77° F) and refers to the maximum amount of average current that can be permitted to flow in the forward direction. If this rating is exceeded, structure breakdown can occur.

**Peak recurrent forward current** is the maximum peak current that can be permitted to flow in the forward direction in the form of recurring pulses.

**Maximum surge current** is the maximum current permitted to flow in the forward direction in the form of nonrecurring pulses. Current should not equal this value for more than a few milliseconds.

**Peak reverse voltage (PRV)** is one of the most important ratings. PRV indicates the maximum reverse-bias voltage that may be applied to a diode without causing junction breakdown. All of the above ratings are subject to change with temperature variations. If, for example, the operating temperature is above that stated for the ratings, the ratings must be decreased.

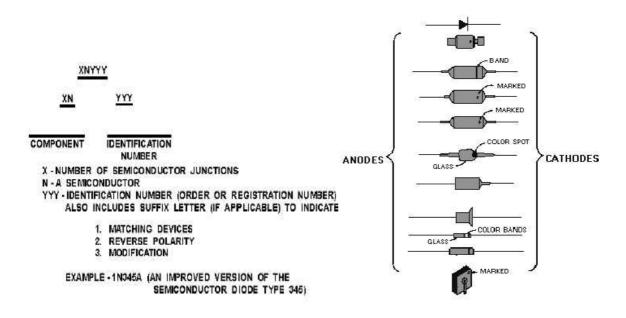

There are many types of diodes varying in size from the size of a pinhead (used in subminiature circuitry) to large 250-ampere diodes (used in high-power circuits). Because there are so many different types of diodes, some system of identification is needed to distinguish one diode from another. This is accomplished with the semiconductor identification system shown in Fig. 4. This system is not only used for diodes but transistors and many other special semiconductor devices as well. As illustrated in this figure, the system uses numbers and letters to identify different types of semiconductor devices. The first number in the system indicates the number of junctions in the semiconductor device and is a number, one less than the number of active elements. Thus 1 designates a diode; 2 designates a transistor (which may be considered as made up of two diodes); and 3 designates a tetrode (a four-element transistor). The letter "N" following the first number indicates a semiconductor. The 2- or 3-digit number following the letter "N" is a serialized identification number. If needed, this number may contain a suffix letter after the last digit. For example, the suffix letter "M" may be used to describe matching pairs of separate semiconductor devices or the letter "R" may be used to indicate reverse polarity. Other letters are used to indicate modified versions of the device which can be substituted for the basic numbered unit. For example, a semiconductor diode designated as type 1N345A signifies a two-element diode (1) of semiconductor material (N) that is an improved version (A) of type 345.

When working with different types of diodes, it is also necessary to distinguish one end of the diode from the other (anode from cathode). For this reason, manufacturers generally code the cathode end of the diode with a "k," "+," "cath," a color dot or band, or by an unusual shape (raised edge or taper) as shown in Fig. 5. In some cases, standard color code bands are placed on the cathode end of the diode. This serves two purposes: (1) it identifies

the cathode end of the diode, and (2) it also serves to identify the diode by number.

#### **Transistors:**

Transistors are identified by a Joint Army-Navy (JAN) designation printed directly on the case of the transistor. If in doubt about a transistor's markings, always replace a transistor with one having identical markings, or consult an equipment or transistor manual to ensure that an identical replacement or substitute is used.

#### **Example:**

| 2                   | Ν             | 130            | А                  |

|---------------------|---------------|----------------|--------------------|

| NUMBER OF JUNCTIONS | SEMICONDUCTOR | IDENTIFICATION | FIRST MODIFICATION |

| (TRANSISTOR)        |               | NUMBER         |                    |

There are three main series of transistor codes used:

- Codes beginning with (or A), for example **BC108**, **BC478** B • The first letter B is for silicon, A is for germanium (rarely used now). The second letter indicates the type; for example C means low power audio frequency; D means high power audio frequency; F means low power high frequency. The rest of the code identifies the particular transistor. There is no obvious logic to the numbering system. Sometimes a letter is added to the end (eg BC108C) to identify a special version of the main type, for example a higher current gain or a different case style. If a project specifies a higher gain version (BC108C) it must be used, but if the general code is given (BC108) any transistor with that code is suitable.

- Codes beginning with TIP, for example TIP31A TIP refers to the manufacturer: Texas Instruments Power transistor. The letter at the end identifies versions with different voltage ratings.

- Codes beginning with 2N, for example 2N3053 The initial '2N' identifies the part as a transistor and the rest of the code identifies the particular transistor. There is no obvious logic to the numbering system.

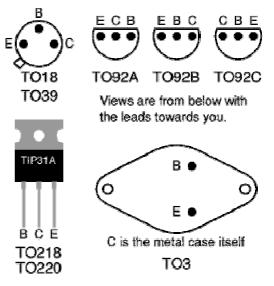

TESTING A TRANSISTOR to determine if it is good or bad can be done with an ohmmeter or transistor tester. PRECAUTIONS should be taken when working with transistors since they are susceptible to damage by electrical overloads, heat, humidity, and radiation. TRANSISTOR LEAD IDENTIFICATION plays an important part in transistor maintenance because before a transistor can be tested or replaced, its leads must be identified. Since there is NO standard method of identifying transistor leads, check some typical lead identification schemes or a transistor manual before attempting to replace transistor. а Identification of leads for some common case styles is shown in Fig. 6.

Fig. 6

## **Testing a transistor**

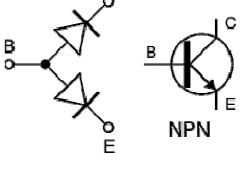

Transistors are basically made up of two *Diodes* connected together back-to-back (Fig. 7). We can use this analogy to determine whether a transistor is of the type PNP or NPN by testing its Resistance between the three different leads, Emitter, Base and Collector.

## Testing with a multimeter

Use a multimeter or a simple tester (battery, resistor and LED) to check each pair of leads for conduction. Set a digital multimeter to diode test and an analogue multimeter to a low resistance range.

Test each pair of leads both ways (six tests in total):

- The **base-emitter** (**BE**) junction should behave like a diode and conduct one way only.

- The **base-collector** (**BC**) junction should behave like a diode and conduct one way only.

Base

• The collector-emitter (CE) should not conduct either way.

Fig. 7: Testing an NPN transistor

R<sub>LOW</sub>

R<sub>HIGH</sub>

The diagram shows how the junctions behave in an NPN transistor. The diodes are reversed in a PNP transistor but the same test procedure can be used.

| Between Trans | sistor Terminals | PNP               | NPN               |

|---------------|------------------|-------------------|-------------------|

| Collector     | Emitter          | R <sub>HIGH</sub> | R <sub>HIGH</sub> |

| Collector     | Base             | R <sub>LOW</sub>  | R <sub>HIGH</sub> |

| Emitter       | Collector        | R <sub>HIGH</sub> | R <sub>HIGH</sub> |

| Emitter       | Base             | R <sub>LOW</sub>  | R <sub>HIGH</sub> |

| Base          | Collector        | R <sub>HIGH</sub> | R <sub>LOW</sub>  |

Emitter

## Transistor Resistance Values for the PNP and NPN transistor types

## **Bipolar Junction Transistor Static Characteristics**

#### **Objective:**

- (i) To study the input and output characteristics of a PNP transistor in Common Base mode and determine transistor parameters.

- (ii) To study the input and output characteristics of an NPN transistor in Common Emitter mode and determine transistor parameters.

#### **Overview:**

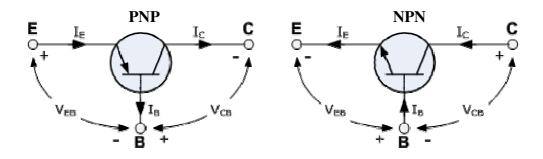

A **Bipolar Junction Transistor**, or **BJT** is a three terminal device having two PN-junctions connected together in series. Each terminal is given a name to identify it and these are known as the Emitter (E), Base (B) and Collector (C). There are two basic types of bipolar transistor construction, NPN and PNP, which basically describes the physical arrangement of the P-type and N-type semiconductor materials from which they are made. Bipolar Transistors are "CURRENT" Amplifying or current regulating devices that control the amount of current flowing through them in proportion to the amount of biasing current applied to their base terminal. The principle of operation of the two transistor types NPN and PNP, is exactly the same the only difference being in the biasing (base current) and the polarity of the power supply for each type.

The symbols for both the NPN and PNP bipolar transistor are shown above along with the direction of conventional current flow. The direction of the arrow in the symbol shows current flow between the base and emitter terminal, pointing from the positive P-type region to the negative N-type region, exactly the same as for the standard diode symbol. For normal operation, the emitter-base junction is forward-biased and the collector-base junction is reverse-biased.

#### **Transistor Configurations**

There are three possible configurations possible when a transistor is connected in a circuit: (a) Common base, (b) Common emitter (c) Common collector. We will be focusing on the first two configurations in this experiment. The behaviour of a transistor can be represented by d.c. current-voltage (I-V) curves, called the static characteristic curves of the device. The three important characteristics of a transistor are: (i) Input characteristics, (ii) Output characteristics and (iii) Transfer Characteristics. These characteristics give information about various transistor parameters, e.g. input and out dynamic resistance, current amplification

factors, etc.

#### **Common Base Transistor Characteristics**

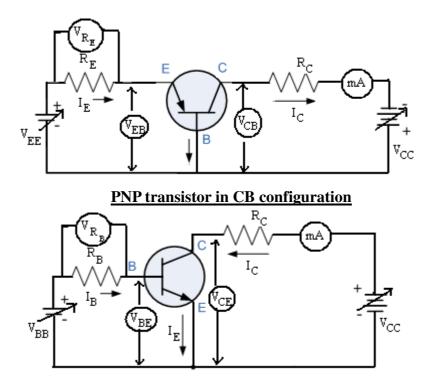

In common base configuration, the base is made common to both input and output as shown in its circuit diagram.

(1) *Input Characteristics:* The input characteristics is obtained by plotting a curve between  $I_E$  and  $V_{EB}$  keeping voltage  $V_{CB}$  constant. This is very similar to that of a forward-biased diode and the slope of the plot at a given operating point gives information about its input dynamic resistance.

**Input Dynamic Resistance** (**r**<sub>i</sub>) This is defined as the ratio of change in base emitter voltage  $(\Delta V_{EB})$  to the resulting change in emitter current  $(\Delta I_E)$  at constant collector-emitter voltage  $(V_{CB})$ . This is dynamic as its value varies with the operating current in the transistor.

$$r_i = \frac{\Delta V_{EB}}{\Delta I_E}\Big|_{V_{CI}}$$

(2) Output Characteristics: The output characteristic curves are plotted between  $I_C$  and  $V_{CB}$ , keeping  $I_E$  constant. The output characteristics are controlled by the input characteristics. Since  $I_C$  changes with  $I_E$ , there will be different output characteristics corresponding to different values of  $I_E$ . These curves are almost horizontal. This shows that the output dynamic resistance, defined below, is very high.

**Output Dynamic Resistance** ( $\mathbf{r}_0$ ): This is defined as the ratio of change in collector-base voltage ( $\Delta V_{CB}$ ) to the change in collector current ( $\Delta I_C$ ) at a constant base current  $I_E$ .

$$r_o = \frac{\Delta V_{CB}}{\Delta I_C} \bigg|_{I_E}$$

(3) *Transfer Characteristics:* The transfer characteristics are plotted between the input and output currents ( $I_E$  versus  $I_C$ ).

#### **Current amplification factor** (α)

This is defined as the ratio of the change in collector current to the change in emitter current at a constant collector-base voltage ( $V_{CB}$ ) when the transistor is in active state.

$$\alpha_{ac} = \frac{\Delta I_{C}}{\Delta I_{E}}\Big|_{V_{CB}}$$

This is also known as small signal current gain and its value is very large. The ratio of  $I_C$  and  $I_E$  is called  $\alpha_{dc}$  of the transistor. Hence,

$$\alpha_{dc} = \frac{I_C}{I_E}\Big|_{V_{CB}}$$

Since I<sub>C</sub> increases with I<sub>E</sub> almost linearly, the values of both  $\alpha_{dc}$  and  $\alpha_{ac}$  are nearly equal.

#### **Common Emitter Transistor Characteristics**

In a common emitter configuration, emitter is common to both input and output as shown in its circuit diagram.

(1) *Input Characteristics:* The variation of the base current  $I_B$  with the base-emitter voltage  $V_{BE}$  keeping the collector-emitter voltage  $V_{CE}$  fixed, gives the input characteristic in CE mode.

**Input Dynamic Resistance** (**r**<sub>i</sub>): This is defined as the ratio of change in base emitter voltage  $(\Delta V_{BE})$  to the resulting change in base current  $(\Delta I_B)$  at constant collector-emitter voltage  $(V_{CE})$ . This is dynamic and it can be seen from the input characteristic, its value varies with the operating current in the transistor:

$$r_i = \frac{\Delta V_{BE}}{\Delta I_B} \bigg|_{V_{CE}}$$

The value of r<sub>i</sub> can be anything from a few hundreds to a few thousand ohms.

(2) Output Characteristics: The variation of the collector current  $I_C$  with the collector-emitter voltage  $V_{CE}$  is called the output characteristic. The plot of  $I_C$  versus  $V_{CE}$  for different fixed values of  $I_B$  gives one output characteristic. Since the collector current changes with the base current, there will be different output characteristics corresponding to different values of  $I_B$ .

**Output Dynamic Resistance** ( $\mathbf{r}_0$ ): This is defined as the ratio of change in collector-emitter voltage ( $\Delta V_{CE}$ ) to the change in collector current ( $\Delta I_C$ ) at a constant base current  $I_B$ .

$$r_o = \frac{\Delta V_{CE}}{\Delta I_C} \bigg|_{I_B}$$

The high magnitude of the output resistance (of the order of 100 kW) is due to the reversebiased state of this diode.

(3) *Transfer Characteristics*: The transfer characteristics are plotted between the input and output currents ( $I_B$  versus  $I_C$ ). Both  $I_B$  and  $I_C$  increase proportionately.

#### Current amplification factor ( $\beta$ )

This is defined as the ratio of the change in collector current to the change in base current at a constant collector-emitter voltage ( $V_{CE}$ ) when the transistor is in active state.

$$\boldsymbol{\beta}_{ac} = \frac{\Delta \boldsymbol{I}_{C}}{\Delta \boldsymbol{I}_{B}}\Big|_{V_{CE}}$$

This is also known as small signal current gain and its value is very large. The ratio of  $I_C$  and  $I_B$  we get what is called  $\beta_{dc}$  of the transistor. Hence,

$$\beta_{dc} = \frac{I_C}{I_B}\Big|_{V_{CE}}$$

Since I<sub>C</sub> increases with I<sub>B</sub> almost linearly, the values of both  $\beta_{dc}$  and  $\beta_{ac}$  are nearly equal.

#### **Circuit components/Equipments:**

(i) Transistors (2 Nos: 1 PNP (CK 100 or equivalent) and 1 NPN (BC 107 or equivalent)), (ii) Resistors (4 Nos.) (iii) Multimeters (3 Nos.), (iv) D.C. power supply, (v) Connecting wires and (vi) Breadboard.

#### **Circuit Diagrams:**

**NPN transistor in CE configuration**

#### **Procedure:**

- 1. Note down the type number of both the transistors.

- 2. Identify different terminals (E, B and C) and the type (PNP/NPN) of the transistors. For any specific information refer the datasheet of the transistors.

#### (I) PNP Common Base (CB) characteristics

- 1. Configure CB circuit using the PNP transistor as per the circuit diagram. Use  $R_E = R_C = 150 \Omega$ .

- 2. For input characteristics, first fix the voltage  $V_{CB}$  by adjusting  $V_{CC}$  to the minimum possible position. Now vary the voltage  $V_{EB}$  slowly (say, in steps of 0.05V) by varying  $V_{EE}$ . Measure  $V_{EB}$  using a multimeter. If  $V_{CB}$  varies during measurement bring it back to the initial set value To determine  $I_E$ , measure  $V_{RE}$  across the resistor  $R_E$  and use the relation  $I_E = V_{RE}/R_E$ .

- 3. Repeat the above step for another value of  $V_{CB}$  say, 2V.

- 4. Take out the multimeter measuring  $V_{EB}$  and connect in series with the output circuit to measure  $I_C$ . For output characteristics, first fix  $I_E = 0$ , i.e.  $V_{RE} = 0$ . By adjusting  $V_{CC}$ , vary the collector voltage  $V_{CB}$  in steps of say 1V and measure  $V_{CB}$  and the corresponding  $I_C$  using multimeters. After acquiring sufficient readings, bring back  $V_{CB}$  to 0 and reduce it further to get negative values. Vary  $V_{CB}$  in negative direction and measure both  $V_{CB}$  and  $I_C$ , till you get 0 current.

- 5. Repeat the above step for at least 5 different values of  $I_E$  by adjusting  $V_{EE}$ . You may need to adjust  $V_{EE}$  continuously during measurement in order to maintain a constant  $I_E$ .

- 6. Plot the input and output characteristics by using the readings taken above and determine the input and output dynamic resistance.

- 7. To plot transfer characteristics, select a suitable voltage  $V_{CB}$  well within the active region of the output characteristics, which you have tabulated already. Plot a graph between  $I_C$  and the corresponding  $I_E$  at the chosen voltage  $V_{CB}$ . Determine  $\alpha_{ac}$  from the slope of this graph.

#### (II) NPN Common Emitter (CE) characteristics

- 1. Now configure CE circuit using the NPN transistor as per the circuit diagram. Use  $R_B = 100k\Omega$  and  $R_C = 1 k\Omega$ .

- 2. For input characteristics, first fix the voltage  $V_{CE}$  by adjusting  $V_{CC}$  to the minimum possible position. Now vary the voltage  $V_{BE}$  slowly (say, in steps of 0.05V) by varying  $V_{BB}$ . Measure  $V_{BE}$  using a multimeter. If  $V_{CE}$  varies during measurement bring it back to the set value To determine  $I_B$ , measure  $V_{RB}$  across the resistor  $R_B$  and use the relation  $I_B = V_{RB}/R_B$ .

- 3. Repeat the above step for another value of  $V_{CE}$  say, 2V.

- 4. For output characteristics, first fix  $I_B = 0$ , i.e.  $V_{RB} = 0$ . By adjusting  $V_{CC}$ , vary the collector voltage  $V_{CE}$  in steps of say 1V and measure  $V_{CE}$  and the corresponding  $I_C$  using multimeters. If needed vary  $V_{CE}$  in negative direction as described for CB configuration and measure both  $V_{CE}$  and  $I_C$ , till you get 0 current.

- 5. Repeat the above step for at least 5 different values of  $I_B$  by adjusting  $V_{BB}$ . You may need to adjust  $V_{BB}$  continuously during measurement in order to maintain a constant  $I_B$ .

- 6. Plot the input and output characteristics by using the readings taken above and determine the input and output dynamic resistance.

- 7. Plot the transfer characteristics between  $I_C$  and  $I_B$  as described for CB configuration for a suitable voltage of  $V_{CE}$  on the output characteristics. Determine  $\beta_{ac}$  from the slope of this graph.

#### **Observations:**

#### **CB** configuration:

Transistor code: \_\_\_\_\_, Transistor type: \_\_\_\_\_ (PNP/NPN)  $R_E$  = \_\_\_\_,  $R_C$  = \_\_\_\_.

#### **Table (1): Input Characteristics**

| Sl. No. | $V_{CB} = \_V$ |             |             | $V_{CB} = \_V$ |  |  |

|---------|----------------|-------------|-------------|----------------|--|--|

|         | $V_{EB}(V)$    | $V_{RE}(V)$ | $I_{E}(mA)$ |                |  |  |

| 1       |                |             |             |                |  |  |

| 2       |                |             |             |                |  |  |

|         |                |             |             |                |  |  |

|         |                |             |             |                |  |  |

| 10      |                |             |             |                |  |  |

#### **Table (2): Output Characteristics**

| Sl. | I <sub>E1</sub> | = 0            | I <sub>E2</sub> | =              | I <sub>E3</sub> | =              | I <sub>E4</sub> | =              | I <sub>E5</sub> | =              |

|-----|-----------------|----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|

| No. | V <sub>CB</sub> | I <sub>C</sub> |

|     | (V)             | (mA)           | <b>(V)</b>      | (mA)           | <b>(V)</b>      | (mA)           | <b>(V)</b>      | (mA)           | (V)             | (mA)           |

| 1   |                 |                |                 |                |                 |                |                 |                |                 |                |

| 2   |                 |                |                 |                |                 |                |                 |                |                 |                |

|     |                 |                |                 |                |                 |                |                 |                |                 |                |

|     |                 |                |                 |                |                 |                |                 |                |                 |                |

| 10  |                 |                |                 |                |                 |                |                 |                |                 |                |

## Table (3): Transfer Characteristics $V_{CB} =$ \_\_\_\_\_V

| Sl. No. | I <sub>E</sub> (mA) | $I_{C}(mA)$ |

|---------|---------------------|-------------|

|         |                     |             |

| 1       |                     |             |

| 2       |                     |             |

| 3       |                     |             |

| 4       |                     |             |

| 5       |                     |             |

| <b>CE configuration:</b> Transistor code:, | Transistor type: | (PNP/NPN) |

|--------------------------------------------|------------------|-----------|

| $R_{\rm B}$ =, $R_{\rm C}$ =               |                  |           |

## Table (5): Input Characteristics

| Sl. No. | $V_{CE} = \_V$ |             |                | $V_{CE} = \_V$ |             |                |

|---------|----------------|-------------|----------------|----------------|-------------|----------------|

|         | $V_{BE}(V)$    | $V_{RB}(V)$ | $I_{B}(\mu A)$ | $V_{BE}(V)$    | $V_{RB}(V)$ | $I_{B}(\mu A)$ |

| 1       |                |             |                |                |             |                |

| 2       |                |             |                |                |             |                |

|         |                |             |                |                |             |                |

|         |                |             |                |                |             |                |

| 10      |                |             |                |                |             |                |

## Table (4): Output Characteristics

| Sl. | I <sub>B1</sub> | = 0            | I <sub>B2</sub> | =              | I <sub>B3</sub> | =                      | I <sub>B4</sub> | =              | I <sub>B5</sub> | =              |

|-----|-----------------|----------------|-----------------|----------------|-----------------|------------------------|-----------------|----------------|-----------------|----------------|

| No. | V <sub>CE</sub> | I <sub>C</sub> | V <sub>CE</sub> | I <sub>C</sub> | V <sub>CE</sub> | I <sub>C</sub><br>(mA) | V <sub>CE</sub> | I <sub>C</sub> | V <sub>CE</sub> | I <sub>C</sub> |

|     | (V)             | (mA)           | <b>(V)</b>      | (mA)           | <b>(V)</b>      | (mA)                   | <b>(V)</b>      | (mA)           | (V)             | (mA)           |

| 1   |                 |                |                 |                |                 |                        |                 |                |                 |                |

| 2   |                 |                |                 |                |                 |                        |                 |                |                 |                |

|     |                 |                |                 |                |                 |                        |                 |                |                 |                |

|     |                 |                |                 |                |                 |                        |                 |                |                 |                |

| 10  |                 |                |                 |                |                 |                        |                 |                |                 |                |

Table (6): Transfer Characteristics $V_{CE} =$ \_\_\_\_\_V

| Sl. No. | $I_{B}\left(\mu A\right)$ | I <sub>C</sub> (mA) |

|---------|---------------------------|---------------------|

| 1       |                           |                     |

| 2       |                           |                     |

| 3       |                           |                     |

| 4       |                           |                     |

| 5       |                           |                     |

## **Graphs:**

Plot the input, output and transfer characteristics for each configuration.

## CB configuration:

- (1) Input characteristics: Plot  $V_{EB} \sim I_E$ , for different  $V_{CB}$  and determine the input dynamic resistance in each case at suitable operating points.

- (2) Output characteristics: Plot  $V_{CB} \sim I_C$ , for different  $I_E$  and determine the output dynamic resistance in each case at suitable operating points in the active region.

- (3) Transfer characteristics: Plot  $I_E \sim I_C$ , for a fixed  $V_{CB}$  and determine  $\alpha_{ac}$ .

## **CE** configuration:

- (1) Input characteristics: Plot  $V_{BE} \sim I_B$ , for different  $V_{CE}$  and determine the input dynamic resistance in each case at suitable operating points.

- (2) Output characteristics: Plot  $V_{CE} \sim I_C$ , for different  $I_B$  and determine the output dynamic resistance in each case at suitable operating points in the active region.

- (3) Transfer characteristics: Plot  $I_B \sim I_C$ , for a fixed  $V_{CE}$  and determine  $\beta_{ac}$ .

#### **Results/Discussions:**

## **Precautions:**

## **Study of Common Emitter Transistor Amplifier circuit**

#### **Objectives:**

1. To design a common emitter transistor (NPN) amplifier circuit.

2. To obtain the frequency response curve of the amplifier and to determine the mid-frequency gain, A<sub>mid</sub>, lower and higher cutoff frequency of the amplifier circuit.

#### **Overview:**

The most common circuit configuration for an NPN transistor is that of the *Common Emitter Amplifier* and that a family of curves known commonly as the *Output Characteristics Curves*, relates the Collector current ( $I_C$ ), to the output or Collector voltage ( $V_{CE}$ ), for different values of Base current ( $I_B$ ). All types of transistor amplifiers operate using AC signal inputs which alternate between a positive value and a negative value. Presetting the amplifier circuit to operate between these two maximum or peak values is achieved using a process known as *Biasing*. Biasing is very important in amplifier design as it establishes the correct operating point of the transistor amplifier ready to receive signals, thereby reducing any distortion to the output signal.

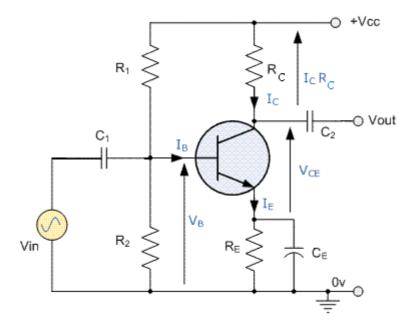

The single stage common emitter amplifier circuit shown below uses what is commonly called "Voltage Divider Biasing". The Base voltage ( $V_B$ ) can be easily calculated using the simple voltage divider formula below:

$$V_B = \frac{V_{CC}R_2}{R_1 + R_2}$$

Thus the base voltage is fixed by biasing and independent of base current provided the current in the divider circuit is large compared to the base current. Thus assuming  $I_B \approx 0$ , one can do the approximate analysis of the voltage divider network without using the transistor

gain,  $\beta$ , in the calculation. Note that the approximate approach can be applied with a high degree of accuracy when the following condition is satisfied:

$$\beta R_E \geq 10R_2$$

#### Load line and Q-point

A static or DC load line can be drawn onto the output characteristics curves of the transistor to show all the possible operating points of the transistor from fully "ON" ( $I_C = V_{CC}/(R_C + R_E)$ ) to fully "OFF" ( $I_C = 0$ ). The quiescent operating point or **Q-point** is a point on this load line which represents the values of  $I_C$  and  $V_{CE}$  that exist in the circuit when no input signal is applied. Knowing  $V_B$ ,  $I_C$  and  $V_{CE}$  can be calculated to locate the operating point of the circuit as follows:

$V_E = V_R - V_{RE}$

$$I_E \approx I_C = \frac{V_E}{R_E}$$

and  $V_{CE} = V_{CC} - I_C (R_C + R_E)$

It can be noted here that the sequence of calculation does not need the knowledge of  $\beta$  and  $I_B$  is not calculated. So the Q-point is stable against any replacement of the transistor.

Since the aim of any small signal amplifier is to generate an amplified input signal at the output with minimum distortion possible, the best position for this Q-point is as close to the centre position of the load line as reasonably possible, thereby producing a Class A type amplifier operation, i.e.  $V_{CE} = 1/2V_{CC}$ .

#### **Coupling and Bypass Capacitors**

In CE amplifier circuits, capacitors  $C_1$  and  $C_2$  are used as Coupling Capacitors to separate the AC signals from the DC biasing voltage. The capacitors will only pass AC signals and block any DC component. Thus they allow coupling of the AC signal into an amplifier stage without disturbing its Q point. The output AC signal is then superimposed on the biasing of the following stages. Also a bypass capacitor,  $C_E$  is included in the Emitter leg circuit. This capacitor is an open circuit component for DC bias, meaning that the biasing currents and voltages are not affected by the addition of the capacitor maintaining a good Q-point stability. However, this bypass capacitor acts as a short circuit path across the emitter resistor at high frequency signals increasing the voltage gain to its maximum. Generally, the value of the bypass capacitor,  $C_E$  is chosen to provide a reactance of at most, 1/10th the value of  $R_E$  at the lowest operating signal frequency.

#### **Amplifier Operation**

Once the Q-point is fixed through DC bias, an AC signal is applied at the input using coupling capacitor  $C_1$ . During positive half cycle of the signal  $V_{BE}$  increases leading to increased  $I_B$ . Therefore  $I_C$  increases by  $\beta$  times leading to decrease in the output voltage,  $V_{CE}$ . Thus the CE amplifier produces an amplified output with a phase reversal. The voltage Gain of the common emitter amplifier is equal to the ratio of the change in the output voltage. Thus,

$$A_{V} = \frac{V_{out}}{V_{in}} = \frac{\Delta V_{CE}}{\Delta V_{BE}}$$

The input  $(Z_i)$  and output  $(Z_o)$  impedances of the circuit can be computed for the case when

the emitter resistor  $R_E$  is completely bypassed by the capacitor,  $C_E$ :  $\mathbf{Z}_i = \mathbf{R}_1 \| \mathbf{R}_2 \| \boldsymbol{\beta} \mathbf{r}_e$  and  $\mathbf{Z}_o = \mathbf{R}_C \| \mathbf{r}_o$

where  $r_e (26mV/I_E)$  and  $r_o$  are the emitter diode resistance and output dynamic resistance (can be determined from output characteristics of transistor). Usually  $r_o \ge 10 R_C$ , thus the gain can be approximated as

$$A_{V} = \frac{V_{out}}{V_{in}} = -\frac{\beta I_{B}(\mathbf{R}_{C} \| \mathbf{r}_{o})}{I_{B} \beta r_{e}} \cong -\frac{R_{C}}{r_{e}}$$

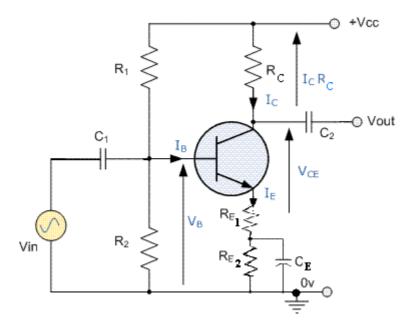

The negative sign accounts for the phase reversal at the output. In the circuit diagram provided below, the emitter resistor is split into two in order to reduce the gain to avoid distortion. So the expression for gain is modified as

$$A_V \cong -\frac{R_{\rm C}}{(R_{E1}+r_e)}$$

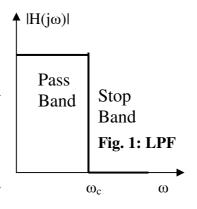

#### **Frequency Response Curve**

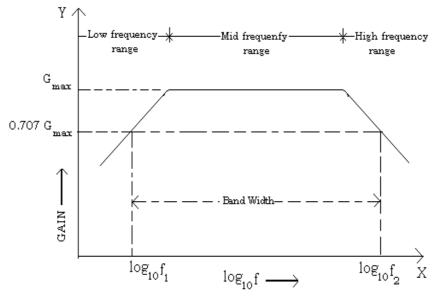

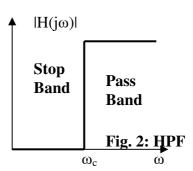

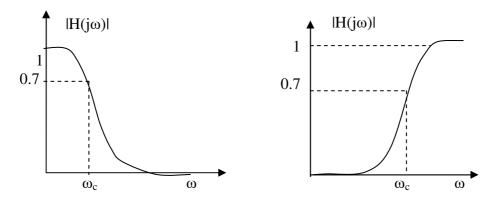

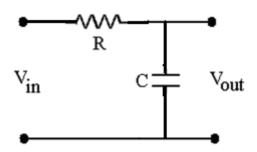

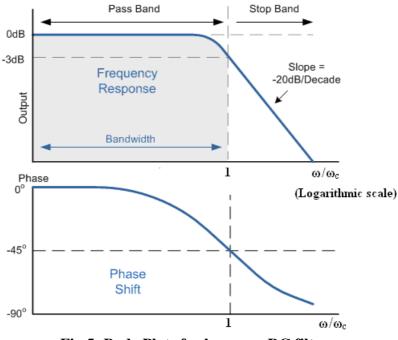

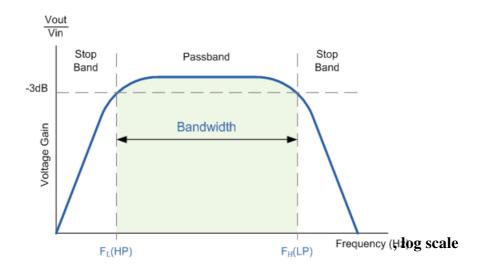

The performance of an amplifier is characterized by its frequency response curve that shows output amplitude (or, more often, voltage gain) plotted versus frequency (often in log scale). Typical plot of the voltage gain of an amplifier versus frequency is shown in the figure below. The frequency response of an amplifier can be divided into three frequency ranges.

The frequency response begins with the lower frequency range designated between 0 Hz and lower cutoff frequency. At lower cutoff frequency, fL, the gain is equal to 0.707 Amid. Amid is a constant mid-band gain obtained from the mid-frequency range. The third, the higher frequency range covers frequency between upper cutoff frequency and above. Similarly, at higher cutoff frequency, fH, the gain is equal to 0.707 Amid. Beyond this the gain decreases with frequency increases and dies off eventually.

#### The Lower Frequency Range

Since the impedance of coupling capacitors increases as frequency decreases, the voltage gain of a BJT amplifier decreases as frequency decreases. At very low frequencies, the capacitive reactance of the coupling capacitors may become large enough to drop some of the input voltage or output voltage. Also, the emitter-bypass capacitor may become large enough

so that it no longer shorts the emitter resistor to ground.

#### The Higher Frequency Range

The capacitive reactance of a capacitor decreases as frequency increases. This can lead to problems for amplifiers used for high-frequency amplification. The ultimate high cutoff frequency of an amplifier is determined by the physical capacitances associated with every component and of the physical wiring. Transistors have internal capacitances that shunt signal paths thus reducing the gain. The high cutoff frequency is related to a shunt time constant formed by resistances and capacitances associated with a node.

#### **Design:**

Before designing the circuit, one needs to know the circuit requirement or specifications. The circuit is normally biased for  $V_{CE}$  at the mid-point of load line with a specified collector current. Also, one needs to know the value of supply voltage  $V_{CC}$  and the range of  $\beta$  for the transistor being used (available in the datasheet of the transistor).

Here the following specifications are used to design the amplifier:

## $V_{CC} = 12V$ and $I_C = 1$ mA

Start by making  $V_E = 0.1 V_{CC}$ . Then  $R_E = V_E/I_E$  (Use  $I_E \approx I_C$ ).

Since  $V_{CE} = 0.5 V_{CC}$ , Voltage across  $R_C = 0.4 V_{CC}$ , i.e.  $R_C = 4.R_E$

In order that the approximation analysis can be applied,  $R_2 \leq 0.1 \beta R_E$ . Here  $\beta$  is the

minimum rated value in the specified range provided by the datasheet (in this case  $\beta = 50$ ).

Finally,

$$R_1 = \frac{V_1}{V_2} R_2$$

,  $V_1$  (=  $V_{CC}-V_2$ ) and  $V_2$  (=  $V_E+V_{BE}$ ) are voltages across  $R_1$  and  $R_2$ ,

respectively.

Based on these guidelines the components are estimated and the nearest commercially available values are used.

#### **Components/ Equipments:**

1. Transistor: CL100 (or equivalent general purpose npn)

2. Resistors:  $R_1$ = 26 (27) K $\Omega$ ,  $R_2$ = 5 (4.7+0.22) K $\Omega$ ,  $R_C$  = 4 (3.9) K $\Omega$ ,  $R_E$ = 1k $\Omega$  ( $R_E$ 1=470  $\Omega$ ,  $R_E$ 2=560  $\Omega$ )

3. Capacitors:  $C_1 = C_2 = 1 \ \mu F$  (2 nos.),  $C_E = 100 \mu F$

- 4. Power Supply ( $V_{CC} = 12V$ )

- 5. Oscilloscope

- 6. Function Generator (~ 100-200 mV pp, sinusoidal for input signal)

- 7. Breadboard

- 8. Connecting wires

#### **Circuit Diagram:**

#### **Procedure:**

- 1. Measure and record all the values of resistance and capacitance and  $\beta$  of the transistor using a multimeter. Configure the circuit as per the diagram.

- 2. Apply supply voltage to the circuit. Measure and record all the dc parameters listed in Table 1 in absence of the ac signal.

- 3. Next, set the function generator in 20Hz "Frequency" range. Also, set the "Attenuation" button at 40dB. Connect the output to the oscilloscope and adjust the "Amplitude" knob till you get a sinusoidal input signal, Vi  $\approx$  100-200 mV peak-to-peak value. DO NOT CHANGE THIS SETTING THROUGHOUT THE EXPERIMENT.

- 4. Now apply this input signal to the circuit you have made keeping the connection to oscilloscope in tact. Feed the output of the circuit to the other channel of oscilloscope. Take care to make all the ground pins common.

- 5. With input signal amplitude always constant, increase signal frequency slowly. Observe, measure and record the output voltage,  $V_o$ . Scan the entire frequency in the range 20 Hz 2 MHz. You may have to measure  $V_i$  and take the ratio  $V_o/V_i$  each time in case input fluctuation is too large to hold constant.

- 6. Calculate the voltage gain for each frequency. Observe the inverted output.

- 7. Plot the frequency response curve, i.e. voltage gain in dB versus frequency on a semi-log graph-sheet.

- 8. Estimate the mid-frequency gain and also the lower and higher cut off frequencies and hence the bandwidth.

#### **Observations:**

$\begin{array}{c} \beta = \_ \\ R_1 = \_ , R_2 = \_ , R_C = \_ , R_E = \_ ; \quad C_1 = \_ , C_2 = \_ , C_E = \_ \\ \end{array}$

Table 1: D.C. analysis of the circuit

| $V_{CC} = 12V$             |                       |                       |  |  |  |

|----------------------------|-----------------------|-----------------------|--|--|--|

| Parameter                  | <b>Computed value</b> | <b>Observed value</b> |  |  |  |

| $V_{B}(V)$                 |                       |                       |  |  |  |

| $V_{E}(V)$                 |                       |                       |  |  |  |

| $I_{C} \approx I_{E} (mA)$ |                       |                       |  |  |  |

| $V_{CE}(V)$                |                       |                       |  |  |  |

| 0                          | • • • • • • • •       | • >                   |  |  |  |

**Q**-point is at (\_\_V, \_\_mA)

## Table 2: Frequency response

$$V_i(pp) = \__m W$$

| Sl.<br>No. | Frequency,<br>f (kHz) | V <sub>0</sub> (pp)<br>(Volt) | $Gain, A_V = \frac{V_o(pp)}{V_i(pp)}$ | Gain<br>(dB) |

|------------|-----------------------|-------------------------------|---------------------------------------|--------------|

| 1          |                       |                               |                                       |              |

| 2          |                       |                               |                                       |              |

|            |                       |                               |                                       |              |

|            |                       |                               |                                       |              |

Calculations:  $r_e = \_$ ,  $Z_i = \_$ ,  $Z_o = \_$ Theoretical value of  $A_v$  in mid-frequency range = \_\_\_\_\_

**Graphs:** Plot the frequency response curve (semi-log plot) and determine the cut-off frequencies, bandwidth and mid- frequency gain.

#### **Discussions:**

#### **Precautions:**

- 1. Vary the input signal frequency slowly.

- 2. Connect electrolytic capacitors carefully.

**Reference:** Electronic devices and circuit theory, Robert L. Boylestad & Louis Nashelsky  $(10^{th} \text{ Edition})$

## **Two Stage RC Coupled Transistor Amplifier**

#### **Objective:**

1. To design a two stage RC coupled common emitter transistor (NPN) amplifier circuit and to study its frequency response curve.

#### **Overview:**

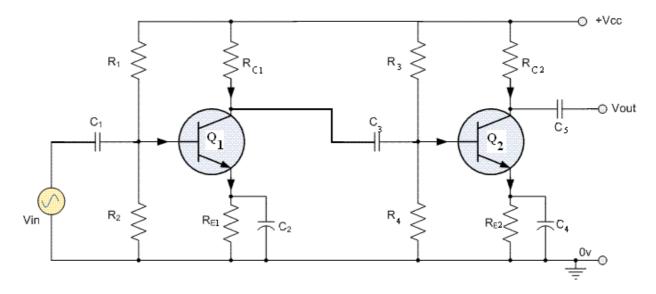

A single stage of amplification is often not enough for a particular application. The overall gain can be increased by using more than one stage, so when two amplifiers are connected in such a way that the output signal of the first serves as the input signal to the second, the amplifiers are said to be connected in *cascade*. The most common arrangement is the common-emitter configuration.

Resistance-capacitance (RC) coupling is most widely used to connect the output of first stage to the input (base) of the second stage and so on. It is the most popular type of coupling because it is cheap and provides a constant amplification over a wide range of frequencies. These R-C coupled amplifier circuits are commonly used as voltage amplifiers in the audio systems.

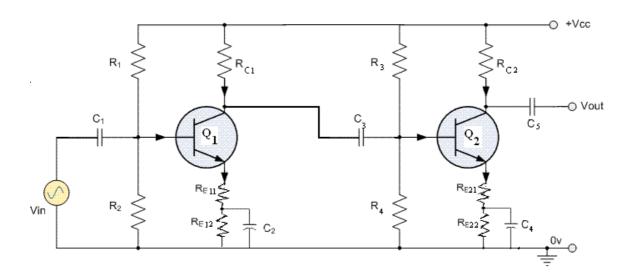

The circuit diagram above shows the 2-stages of an R-C coupled amplifier in CE configuration using NPN transistors. Capacitors  $C_1$  and  $C_3$  couple the input signal to transistors  $Q_1$  and  $Q_2$ , respectively.  $C_5$  is used for coupling the signal from  $Q_2$  to its load.  $R_1$ ,  $R_2$ ,  $R_{E1}$  and  $R_3$ ,  $R_4$ ,  $R_{E2}$  are used for biasing and stabilization of stage 1 and 2 of the amplifier.  $C_2$  and  $C_4$  provide low reactance paths to the signal through the emitter.

#### **Overall gain:**

The total gain of a 2-stage amplifier is equal to the product of individual gain of each stage. (You may refer to the handout for single stage amplifier to calculate individual gain of the stages.) Once the second stage is added, its input impedance acts as an additional load on the first stage thereby reducing the gain as compared to its no load gain. Thus the overall gain characteristics is affected due to this loading effect.

The loading of the second stage i.e. input impedance of second stage,  $\mathbf{Z}_{i2} = \mathbf{R}_3 \| \mathbf{R}_4 \| \boldsymbol{\beta} \mathbf{r}_{e2}$

Thus loaded gain of the first stage,  $A_{V1} = -\frac{R_{C1} \|Z_{i2}\|}{r}$

and the unloaded gain of second stage,

$$A_{V2} = -\frac{R_{C2}}{r_{e2}}$$

In the circuit diagram provided below, the emitter resistor is split into two in order to reduce the gain to avoid distortion. So the expression for gain each stage is modified as

$$A_{V1} = -\frac{R_{C1} \| Z_{i2}}{(R_{E1} + r_{e1})}$$

$$A_{V2} = -\frac{R_{C2}}{R_{E2} + r_{e2}}$$

The overall gain of the 2 stage amplifier is  $A_V = A_{V1} \times A_{V2}$ .

#### **Frequency Response Curve**

The performance of an amplifier is characterized by its frequency response curve that shows voltage gain (often expressed in dB units) plotted versus frequency. The frequency response begins with the lower frequency region designated between 0 Hz and lower cutoff frequency. At lower cutoff frequency, fL, the gain is equal to 0.707 Amid. Amid is a constant mid-band gain obtained from the mid-band frequency region. The third, the upper frequency region covers frequency between upper cutoff frequency and above. Similarly, at upper cutoff frequency, fH, the gain is equal to 0.707 Amid. Beyond the upper cutoff frequency, the gain decreases as the frequency increases and dies off eventually. (More details are given in the hand out for single stage amplifier.)

Design: The design details are already given in the single stage amplifier hand out.

#### **Components/ Equipments:**

- 1. Transistor: CL100 (or equivalent general purpose npn, 2 nos)

- 2. Resistors:  $R_1$ ,  $R_3 = 26$  (27) K $\Omega$ ,  $R_2$ ,  $R_4 = 5$  (4.7+0.22) K $\Omega$ ,  $R_{C1}$ ,  $R_{C2} = 4$  (3.9) K $\Omega$ ,  $R_{E1}$ ,  $R_{E2} = 100$  (2.1)

- 1kΩ (R<sub>E11</sub>, R<sub>E21</sub>=470 Ω; R<sub>E12</sub>, R<sub>E22</sub>=560 Ω) (2 nos. of each resistance value)

- 3. Capacitors:  $C_1 = C_3 = C_5 = 1 \ \mu F$  (3 nos.),  $C_2 = C_4 = 100 \mu F$  (2 nos.)

- 4. Power Supply ( $V_{CC} = 12V$ )

- 5. Oscilloscope

- 6. Function Generator (~ 100-200 mV pp, sinusoidal for input signal)

- 7. Breadboard

- 8. Connecting wires

## **Circuit Diagram:**

#### **Procedure:**

- 1. Measure and record all the values of resistance and capacitance and  $\beta$  of the transistor using a multimeter. Configure the circuit as per the diagram. Make a provision so that the two stages can either be separated or connected as and when required.

- 2. Apply supply voltage to the circuit. Measure and record all the dc parameters of each individual stage separately as listed in Table 1 in absence of the ac signal.

- 3. Next, set the function generator at 20kHz by putting the frequency knob in 20KHz range and adjusting the variable knob. Also, set the "Attenuation" button at 40dB. Connect the output to the oscilloscope and adjust the "Amplitude" knob till you get a sinusoidal input signal, Vi  $\approx$  100-200 mV peak-to-peak value. DO NOT CHANGE THIS SETTING THROUGHOUT THE EXPERIMENT.

- 4. To fill up first row of Table 2 the two stages should be separated. Now apply the input signal to the circuit at the first stage keeping the connection to oscilloscope intact. Feed the output of the first stage to the other channel of oscilloscope. Take care to make all the ground pins common. Measure the output and calculate unloaded gain of stage 1.

- 5. Similarly by applying input at the second stage measure the output and calculate the unloaded gain of second stage.

- 6. For the second row of Table 2, connect the two stages. Apply the input signal at the first stage Measure the output of first stage and calculate its loaded gain.

- 7. Now, with the input signal at the first stage, measure the output at the second stage and calculate the total gain of the two stage amplifier and complete Table-2.

- 8. To study the frequency response of the two stage amplifier, vary the input signal frequency in the range 20 Hz 2 MHz, keeping the input signal amplitude always constant. Observe measure and record the output voltage,  $V_o$  at the second stage. (You may have to measure  $V_i$  and take the ratio  $V_o/V_i$  each time in case input fluctuation is too large to hold constant.) Calculate voltage gain for each frequency.

- 9. Plot the frequency response curve, i.e. voltage gain in dB versus frequency on a semi-log graph-sheet.

- 10. Estimate the mid-frequency gain and also the lower and higher cut off frequencies and hence the bandwidth.

**Observations:**

β1 = \_\_\_\_\_, β2 = \_\_\_\_\_

**Stage 1:**  $R_1$ = \_\_\_\_,  $R_2$ = \_\_\_\_,  $R_C$ = \_\_\_\_,  $R_E$ = \_\_\_+\_\_;  $C_1$ = \_\_\_,  $C_2$ = \_\_\_,  $C_E$ = \_\_\_\_ **Stage 2:**  $R_1$ = \_\_\_\_,  $R_2$ = \_\_\_\_,  $R_C$ = \_\_\_\_,  $R_E$ = \_\_\_+\_\_;  $C_1$ = \_\_\_,  $C_2$ = \_\_\_,  $C_E$ = \_\_\_\_

Table 1: D.C. analysis of the circuit

$V_{CC} = 12V$

| Parameter                  | Stage 1 (Q1)   |                       | Stage 2 (Q2)          |                       |

|----------------------------|----------------|-----------------------|-----------------------|-----------------------|

|                            | Computed value | <b>Observed value</b> | <b>Computed value</b> | <b>Observed value</b> |

| $V_{B}(V)$                 |                |                       |                       |                       |

| $V_{E}(V)$                 |                |                       |                       |                       |

| $I_{C} \approx I_{E} (mA)$ |                |                       |                       |                       |

| $V_{CE}(V)$                |                |                       |                       |                       |

| $r_e(\Omega)$              |                |                       |                       |                       |

| Q-point                    |                |                       |                       |                       |

Table 2: Mid frequency voltage Gain ( $f \approx 20$  kHz)

Vi = \_\_\_\_\_

| Parameter    | Stage 1 (Q1) |          | Stage 2 (Q2) |          |

|--------------|--------------|----------|--------------|----------|

|              | Computed     | Measured | Computed     | Measured |

| Unloaded     |              |          |              |          |

| Voltage Gain |              |          |              |          |

| $(V_o/V_i)$  |              |          |              |          |

| Loaded       |              |          |              |          |

| Voltage Gain |              |          |              |          |

Total mid frequency gain = Loaded Voltage Gain  $(Q1) \times$  Unloaded Voltage Gain (Q2)

Total gain (computed) = \_\_\_\_\_

Total gain (measured) = \_\_\_\_\_

Table 3: Frequency Response

V<sub>i</sub>(pp) = \_\_\_\_\_

| Sl. | Frequency, | V <sub>0</sub> (pp) | $Gain, A_V = \frac{V_o(pp)}{V_i(pp)}$ | Gain |

|-----|------------|---------------------|---------------------------------------|------|

| No. | f (kHz)    | (Volt)              |                                       | (dB) |

| 1   |            |                     |                                       |      |

| 2 |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

Calculations: Stage 1: Z<sub>i1</sub> = \_\_\_\_\_, Z<sub>01</sub> = \_\_\_\_\_

Stage 2:  $Z_{i2} = \_, Z_{o2} = \_$

**Graphs:** Plot the frequency response curve and determine the cut-off frequencies, bandwidth and mid-band gain.

## **Discussions:**

#### **Precautions:**

- 3. Vary the input signal frequency slowly.

- 4. Connect electrolytic capacitors carefully.

**Reference:** Electronic devices and circuit theory, Robert L. Boylestad & Louis Nashelsky  $(10^{th} \text{ Edition})$

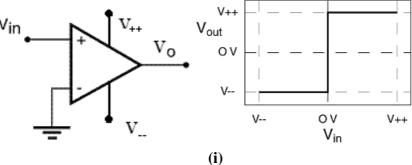

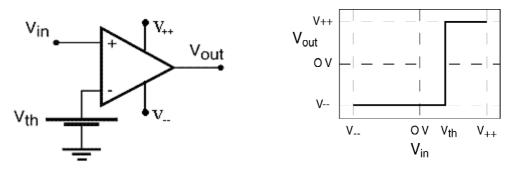

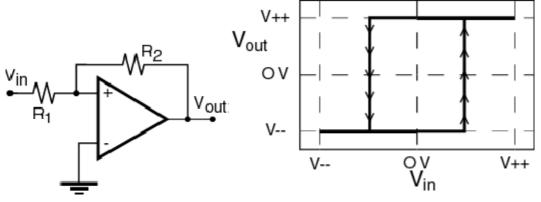

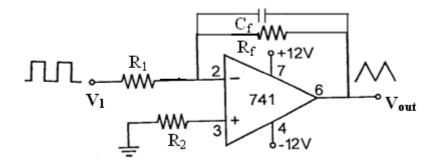

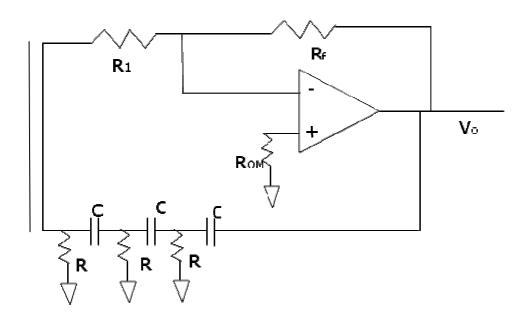

## **Operational Amplifiers** (Supplementary note)

#### **Ideal Operational Amplifier**

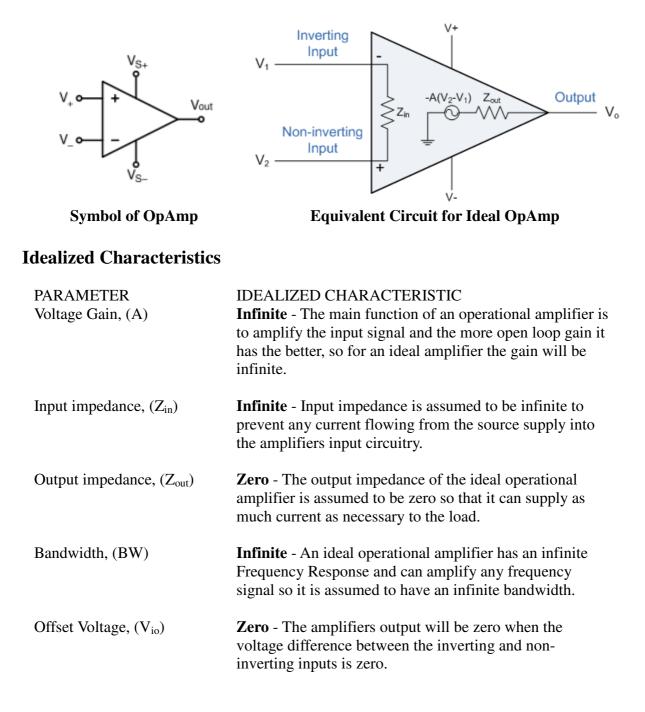

As well as resistors and capacitors, **Operational Amplifiers**, or **Op-amps** as they are more commonly called, are one of the basic building blocks of Analogue Electronic Circuits. It is a linear device that has all the properties required for nearly ideal DC amplification and is used extensively in signal conditioning, filtering or to perform mathematical operations such as add, subtract, integration and differentiation. An ideal operational amplifier is basically a 3-terminal device that consists of two high impedance inputs, one an **Inverting input** marked with a negative sign, ("-") and the other a **Non-inverting input** marked with a positive plus sign ("+").

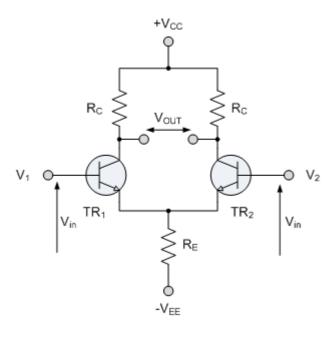

The amplified output signal of an Operational Amplifier is the difference between the two signals being applied to the two inputs. In other words the output signal is a *differential* signal between the two inputs and the input stage of an Operational Amplifier is in fact a differential amplifier as shown below.

#### **Differential Amplifier**

The circuit shows a generalized form of a differential amplifier with two inputs marked  $V_1$  and  $V_2$ . The two identical transistors  $TR_1$ and TR<sub>2</sub> are both biased at the same operating point with their emitters connected together and returned to the common rail, - $V_{EE}$  by way of resistor  $R_E$ . The circuit operates from a dual supply  $+V_{CC}$  and  $-V_{EE}$ which ensures a constant supply. As the two base inputs are out of phase with each other, the output voltage, V<sub>OUT</sub>, is the difference between the two input signals. So, as the forward bias of transistor TR<sub>1</sub> is increased, the forward bias of transistor TR<sub>2</sub> is reduced and vice versa. Then if the two transistors are perfectly matched, the current flowing through the common emitter resistor, R<sub>E</sub> will remain constant.

Ideal Operational Amplifiers have an output of low impedance that is referenced to a common ground terminal and it should ignore any common mode signals. That means, if identical signals are applied to both the inverting and non-inverting inputs there should be no change at the output. However, in real amplifiers there is always some variation and the ratio of the change to the output voltage with regards to the change in the common mode input voltage is called the **Common Mode Rejection Ratio** or **CMRR**.

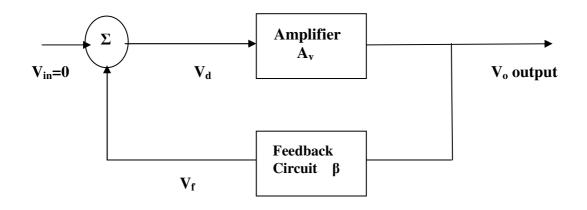

Operational Amplifiers have a very high open loop DC gain, commonly known as the

**Open Loop Differential Gain**, and is given the symbol  $(A_o)$ . By applying some form of **Negative Feedback** we can produce an operational amplifier circuit with a very precise gain characteristic that is dependent only on the feedback used. An operational amplifier only responds to the difference between the voltages at its two input terminals, known commonly as the "*Differential Input Voltage*" and not to their common potential. Then if the same voltage potential is applied to both terminals the resultant output will be zero.

It is important to remember two properties known as the **golden rules**, as they help understand the working of the amplifier with regards to analysis and design of operational amplifier circuits.

- 1. No current flows into either input terminal (the current rule)

- 2. The differential input offset voltage is zero (the voltage rule).

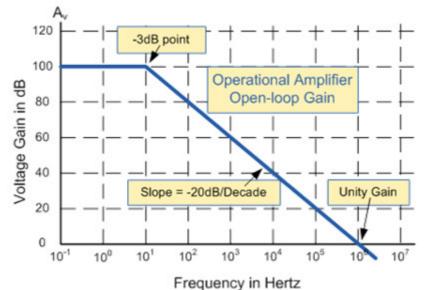

However, real **Operational Amplifiers** (e.g. 741) do not have infinite gain or bandwidth but have a typical "Open Loop Gain" which is defined as the amplifiers output amplification without any external feedback signals connected to it and for a typical operational amplifier is about 100dB at DC (zero Hz). This output gain decreases linearly with frequency down to "Unity Gain" or 1, at about 1MHz and this is shown in the following open loop gain response curve. From this frequency response curve we can see that the product of the gain against frequency is constant at any point along the curve. Also that the unity gain (0dB) frequency also determines the gain of the amplifier at any point along the curve. This constant is generally known as the **Gain Bandwidth Product** or **GBP**. Therefore, GBP = Gain × Bandwidth or A × BW.

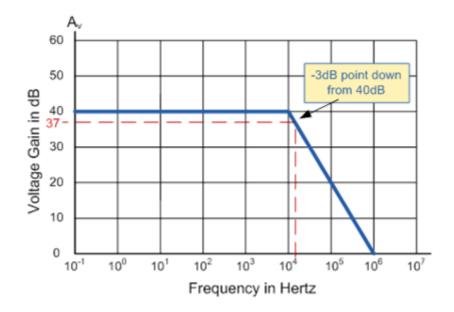

#### **Open-loop Frequency Response Curve**

For example, from the graph above the gain of the amplifier at 100kHz = 20dB or 10, then the

GBP = 100,000Hz x 10 = 1,000,000.

Similarly, a gain at 1kHz = 60dB or 1000, therefore the GBP = 1,000 x 1,000 = 1,000,000. The same!.

The Voltage Gain (A) of the amplifier can be found using the following formula:

$$Gain, A = \frac{V_o}{V_i}$$

and in **Decibels** or (dB) is given as:

$$20\log A = 20\log \frac{V_o}{V_i}$$

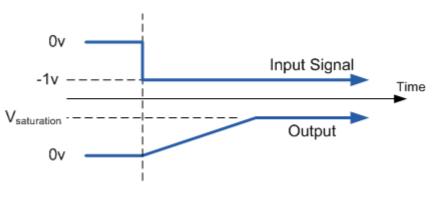

#### **Bandwidth of Operational Amplifier**

The operational amplifiers bandwidth is the frequency range over which the voltage gain of the amplifier is above 70.7% or -3dB (where 0dB is the maximum) of its maximum output value as shown below.

Here we have used the 40dB line as an example. The -3dB or 70.7% of  $V_{max}$  down point from the frequency response curve is given as 37dB. Taking a line across until it intersects with the main GBP curve gives us a frequency point just above the 10kHz line at about 12 to 15kHz. We can now calculate this more accurately as we already know the GBP of the amplifier, in this particular case 1MHz.

#### **Example No1.**

Using the formula 20 log (A), we can calculate the bandwidth of the amplifier as:

$37 = 20 \log A$  therefore,  $A = anti-log (37 \div 20) = 70.8$

GBP  $\div$  A = Bandwidth, therefore, 1,000,000  $\div$  70.8 = 14.124Hz, or 14kHz

Then the bandwidth of the amplifier at a gain of 40dB is given as **14kHz** as predicted from the graph.

#### Example No2.

If the gain of the operational amplifier was reduced by half to say **20dB** in the above frequency response curve, the -3dB point would now be at 17dB. This would then give us an overall gain of 7.08, therefore A = 7.08. If we use the same formula as above this new gain would give us a bandwidth of **141.2kHz**, ten times more than at 40dB.

It can therefore be seen that by reducing the overall open loop gain of an operational amplifier its bandwidth is increased and vice versa. The -3dB point is also known as the "half power point", as the output power of the amplifier is at half its maximum value at this point.

## **Op-amp types**

Operational amplifiers can be connected using external resistors or capacitors in a number of different ways to form basic "Building Block" circuits such as, Inverting, Non-

Inverting, Voltage Follower, Summing, Differential, Integrator and Differentiator type amplifiers. There are a very large number of operational amplifier IC's available to suit every possible application.

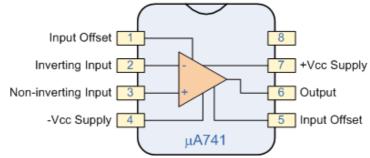

The most commonly available and used of all operational amplifiers is the industry standard **741** type IC.

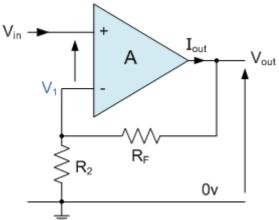

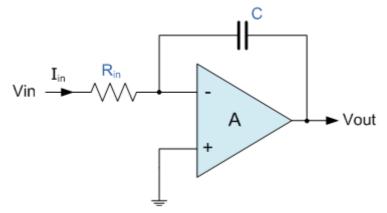

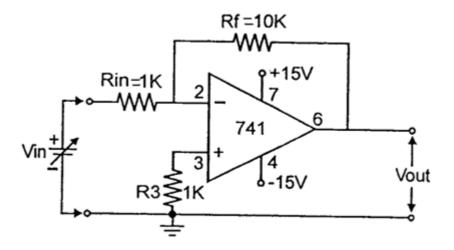

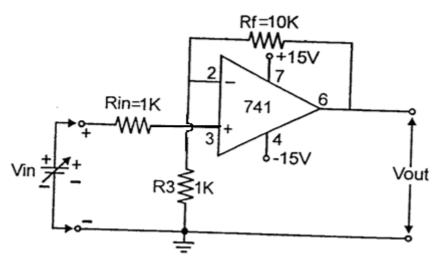

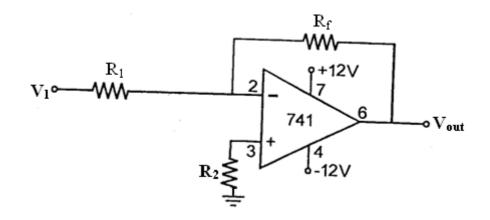

#### **Inverting Amplifier**

The open loop gain of an ideal Operational Amplifier can be very high, up to about 1,000,000 (120dB) or more. However, this very high gain is of no real use to us as it makes the amplifier both unstable and hard to control as the smallest of input signals, just a few micro-volts, would be enough to cause the output to saturate and swing towards one or the other of the voltage supply rails losing control. As the open loop DC gain of an operational amplifier is extremely high we can afford to lose some of this gain by connecting a suitable resistor across the amplifier from the output terminal back to the inverting input terminal to both reduce and control the overall gain of the amplifier. This then produces an effect known commonly as **Negative Feedback**, and thus produces a very stable Operational Amplifier system.

**Negative Feedback** is the process of "feeding back" some of the output signal back to the input, but to make the feedback negative we must feed it back to the "Negative input" terminal using an external **Feedback Resistor** called  $R_f$ . This feedback connection between the output and the inverting input terminal produces a closed loop circuit to the amplifier resulting in the gain of the amplifier now being called its **Closed-loop Gain**.

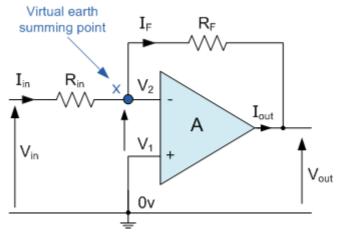

This results in the inverting input terminal having a different signal on it than the actual input voltage as it will be the sum of the input voltage plus the negative feedback voltage giving it the label or term of a *Summing Point*. We must therefore separate the real input signal from the inverting input by using an **Input Resistor**, R<sub>in</sub>. As we are not using the positive non-inverting input this is connected to a common ground or zero voltage terminal as shown below. But the effect of this closed loop feedback circuit results in the voltage at the inverting input equal to that at the non-inverting input producing a *Virtual Earth* summing point because it will be at the same potential as the grounded reference input.

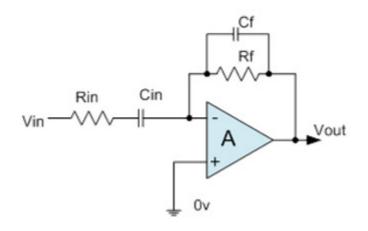

#### **Inverting Amplifier Circuit**

In inverting amplifier circuit the operational amplifier is connected with feedback to produce a closed loop operation. There are two very important rules to remember about inverting amplifiers: "no current flows into the input terminal" and that " $V_1$  equals  $V_2$ ". This is because the junction of the input and feedback signal (X) is at the same potential as the positive (+) input which is at zero volts or ground then, the junction is a "**Virtual Earth**". Because of this virtual earth node the input resistance of the amplifier is equal to the value of the input resistor,  $R_{in}$ . Then by using these two rules one can find the equation for calculating the gain of an inverting amplifier, using first principles.

Current (i) flows through the resistor network as shown.

$$i = \frac{V_{in}}{R_{in}} = -\frac{V_o}{R_f} \qquad \qquad V_{in} \stackrel{i}{\longrightarrow} V_2 = 0 \qquad \qquad V_{out}$$

The negative sign in the equation indicates an inversion of the output signal with respect to the input as it is 180° out of phase. This is due to the feedback being negative in value. Then, the **Closed-Loop Voltage Gain** of an Inverting Amplifier is given as.

$$Gain = \frac{V_o}{V_{in}} = -\frac{R_f}{R_{in}}$$

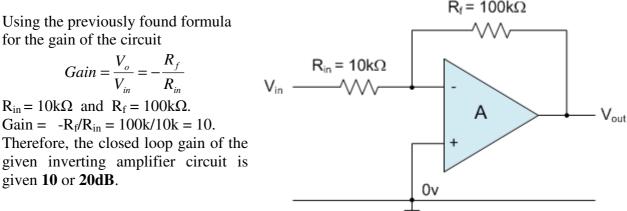

#### **Example No1**

Find the closed loop gain of the given inverting amplifier circuit.

#### Example No2.

The gain of the original circuit is to be increased to 40, find the new values of the resistors required.

Assume that the input resistor is to remain at the same value of  $10K\Omega$ , then by re-arranging the closed loop voltage gain formula we can find the new value required for the feedback

resistor  $R_f$ .  $Gain = -R_f/R_{in}$ So,  $R_f = Gain \times R_{in}$   $Rf = 400,000 \text{ or } 400K\Omega$ The new values of resistors required for the circuit to have a gain of **40** would be,  $R_{in} = 10K\Omega$  and  $R_f = 400K\Omega$ . The formula could also be rearranged to give a new value of  $R_{in}$ , keeping the same value of  $R_f$ .

#### **Unity Gain Inverter**

One final point to note about **Inverting Amplifiers**, if the two resistors are of equal value,  $R_{in} = R_f$  then the gain of the amplifier will be **-1** producing a complementary form of the input voltage at its output as  $V_{out} = -V_{in}$ . This type of inverting amplifier configuration is generally called a **Unity Gain Inverter** of simply an *Inverting Buffer*.

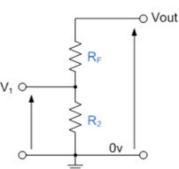

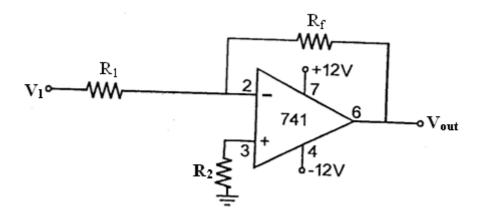

## **Non-inverting Amplifier**

The second basic configuration of an operational amplifier circuit is that of a **Non-inverting Amplifier**. In this configuration, the input voltage signal,  $(V_{in})$  is applied directly to the Non-inverting (+) input terminal which means that the output gain of the amplifier becomes "Positive" in value in contrast to the "Inverting Amplifier" circuit whose output gain is negative in value. Feedback control of the non-inverting amplifier is achieved by applying a small part of the output voltage signal back to the inverting (-) input terminal via a  $R_f - R_2$  voltage divider network, again producing negative feedback. This produces a Non-inverting Amplifier circuit with very good stability, a very high input impedance,  $R_{in}$  approaching infinity (as no current flows into the positive input terminal) and a low output impedance,  $r_{out}$  as shown below.

#### Non-inverting Amplifier Circuit

Since no current flows into the input of the amplifier,  $V_1 = V_{in}$ . In other words the junction is a "**Virtual Earth**" summing point. Because of this virtual earth node, the resistors  $R_f$  and  $R_2$  form a simple voltage divider network across the amplifier and the voltage gain of the circuit is determined by the ratios of  $R_2$  and  $R_f$  as shown below.

#### **Equivalent Voltage Divider Network**

Then using the formula to calculate the output voltage of a potential divider network, we can calculate the output Voltage

Gain of the Non-inverting Amplifier as:

$$V_0 = V_{in} (1 + \frac{R_f}{R_2})$$

$$Gain = \frac{V_o}{V_{in}} = 1 + \frac{R_f}{R_2}$$

We can see that the overall gain of a Non-Inverting Amplifier is greater but never less than 1, is positive and is determined by the ratio of the values of  $R_f$  and  $R_2$ . If the feedback resistor  $R_f$  is zero the gain will be equal to 1, and if resistor  $R_2$  is zero the gain will approach infinity, but in practice it will be limited to the operational amplifiers open-loop differential gain, ( $A_o$ ).

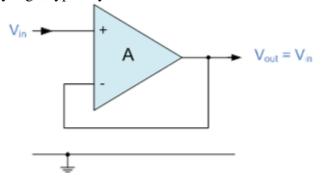

#### **Voltage Follower (Unity Gain Buffer)**

If we made the feedback resistor,  $R_f = 0$  then the circuit will have a fixed gain of "1" and would be classed as a **Voltage Follower**. As the input signal is connected directly to the non-inverting input of the amplifier the output signal is not inverted resulting in the output voltage being equal to the input voltage,  $V_{out} = V_{in}$ . This then makes the Voltage Follower circuit ideal as a *Unity Gain Buffer* circuit because of its isolation properties as impedance or circuit isolation is more important than amplification. The input impedance of the voltage follower circuit is very high, typically above  $1M\Omega$ .

In this circuit,  $R_{in}$  has increased to infinity and  $R_f$  reduced to zero, the feedback is 100% and  $V_{out}$  is exactly equal to  $V_{in}$  giving it a fixed gain of 1 or unity. As the input voltage  $V_{in}$  is applied to the non-inverting input the gain of the amplifier is given as:

$$V_o = A(V_{in} - V_o)$$

$$V_{in} = V_+ \quad V_o = V_-$$

$$Gain = \frac{V_o}{V_{in}} = 1$$

The voltage follower or unity gain buffer is a special and very useful type of **Non-inverting amplifier** circuit that is commonly used in electronics to isolate circuits from each other especially in High-order state variable or Sallen-Key type active filters to separate one filter stage from the other. Typical digital buffer IC's available are the 74LS125 Quad 3-state buffer or the more common 74LS244 Octal buffer.

One final thought, the output voltage gain of the voltage follower circuit with closed loop gain is **Unity**, the voltage gain of an ideal operational amplifier with open loop gain (no feedback) is infinite. Then by carefully selecting the feedback components we can control the amount of gain produced by an Operational Amplifier anywhere from 1 to infinity.

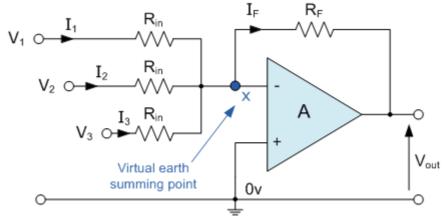

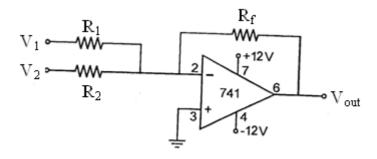

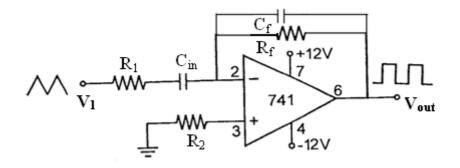

#### **Summing Amplifier**

The **Summing Amplifier** is a very flexible circuit based upon the standard *Inverting Operational Amplifier* configuration. We saw previously that the inverting amplifier has a single input signal applied to the inverting input terminal. If we add another input resistor equal in value to the original input resistor, R<sub>in</sub> we end up with another operational amplifier circuit called a **Summing Amplifier**, "*Summing Inverter*" or even a "*Voltage Adder*" circuit as shown below

## **Summing Amplifier Circuit**

The output voltage,  $(V_{out})$  now becomes proportional to the sum of the input voltages,  $V_1$ ,  $V_2$ ,  $V_3$  etc. Then we can modify the original equation for the inverting amplifier to take account of these new inputs thus:

$$I_{F} = I_{1} + I_{2} + I_{3} = -\left[\frac{V_{1}}{R_{in}} + \frac{V_{2}}{R_{in}} + \frac{V_{3}}{R_{in}}\right]$$

then,  $V_{out} = -\frac{R_{F}}{R_{in}}(V_{1} + V_{2} + V_{3})$

The **Summing Amplifier** is a very flexible circuit indeed, enabling us to effectively "Add" or "Sum" together several individual input signals. If the input resistors are all equal a unity gain inverting adder can be made. However, if the input resistors are of different values a "scaling summing amplifier" is produced which gives a weighted sum of the input signals.

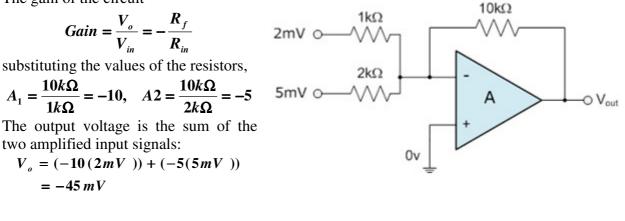

#### **Example No1**

Find the output voltage of the following *Summing Amplifier* circuit. The gain of the circuit

If the input resistances of a summing amplifier are connected to potentiometers the individual input signals can be mixed together by varying amounts. For example, for measuring temperature, you could add a negative offset voltage to make the display read "0" at the freezing point or produce an audio mixer for adding or mixing together individual waveforms (sounds) from different source channels (vocals, instruments, etc) before sending them combined to an audio amplifier.

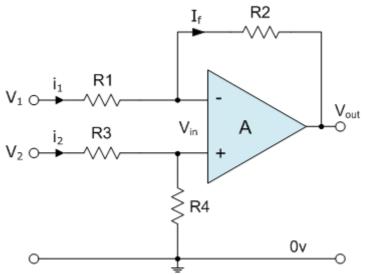

#### **Differential Amplifier**

Up to now we have used only one input to connect to the amplifier, using either the "Inverting" or the "Non-inverting" input terminal to amplify a single input signal with the other input being connected to ground. But we can also connect signals to both of the inputs at the same time producing another common type of operational amplifier circuit called a differential amplifier.

The resultant output voltage will be proportional to the "Difference" between the two input signals,  $V_1$  and  $V_2$ . This type of circuit can also be used as a subtractor.

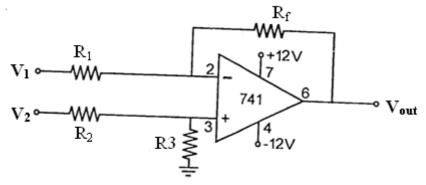

## Differential Amplifier Circuit

The transfer function for a differential amplifier circuit is given as:

$$V_o = -\frac{R_2}{R_1}V_1 + (1 + \frac{R_2}{R_1})(\frac{R_4}{R_3 + R_4})V_2$$

When R1 = R3 and R2 = R4 the transfer function formula can be modified to the following:

$$V_o = \frac{R_2}{R_1} (V_2 - V_1)$$

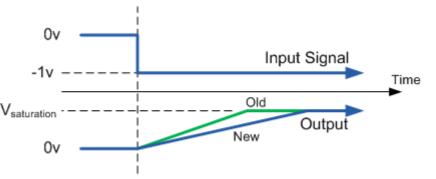

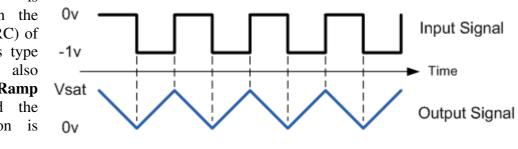

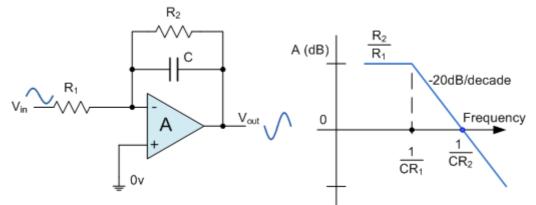

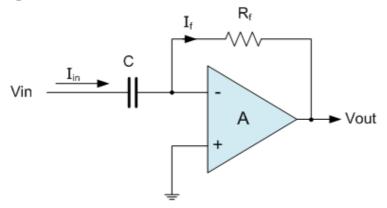

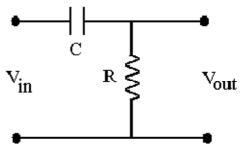

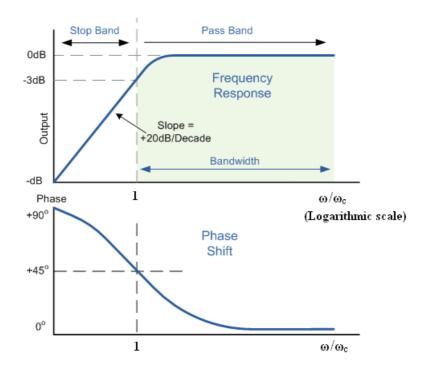

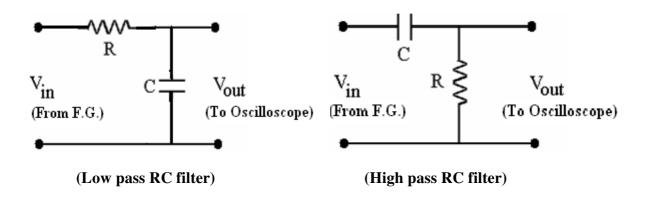

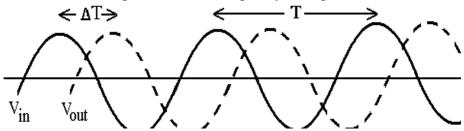

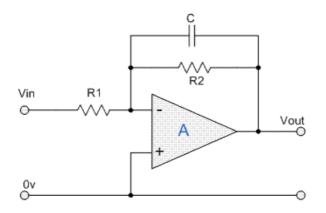

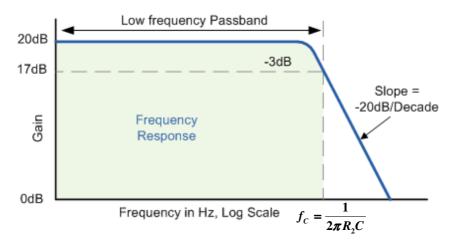

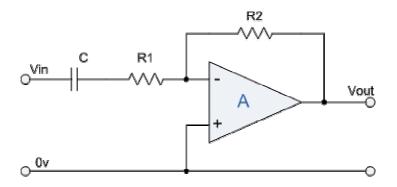

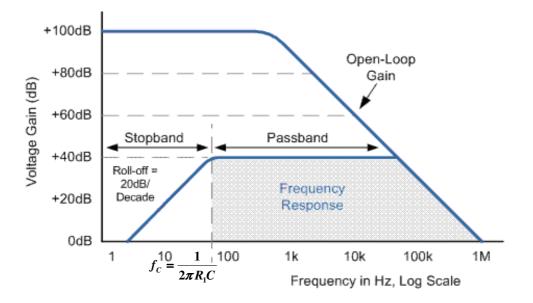

If all the resistors are all of the same ohmic value the circuit will become a **Unity Gain Differential Amplifier** and the gain of the amplifier will be 1 or Unity.